单片机的pin输入高电平为什么要加一个拉电阻?单片机引脚内部上拉是什么意思?请先了解什么是上拉阻力。你说的单片机引脚内部上拉,是指集成电路内部可以实现上拉电阻,51单片机的P0口为什么要接一个拉电阻?从零开始学51单片机2什么是上拉电阻?单片机上连接下拉电阻的引脚的作用及连接图因为单片机的输出端是开漏输出,就像三极管的集电极一样,没有上拉电阻就不能输出高电平。

1、c51单片机的普通io口为什么要加一个上拉电阻呢P0的开漏io口为什么也要…

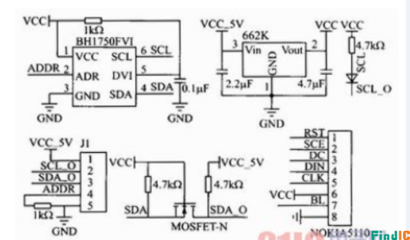

1,c51单片机内部除P0口外都有上拉电阻,不过这个很老了,现在都有上拉电阻了;如建筑主图所示,虽然内部有上拉电阻,但作为设计者,大家都希望将输入端设置为高电平,用于读取信号,当有低电平时,可以采集;p0灯的连接由高电平的外部上拉电阻触发。P2是一个内部弱引体向上,当它暂停时,它是一个高水平的引体向上。因为你的说法是p0p2,p0也是高电平,所以灯不亮。

旧的51P0端口作为总线使用,不需要上拉。如果用作输出端口,不上拉就没有高电平。对于其他端口,上拉电流只能达到160微安,推不动大负载,所以有时会加一个上拉电阻。如果低级别有效,则可以不添加。为了PCB设计的方便(比如LED显示屏),往往会留下上拉电阻的位置。目前,51端口有四种设置。设置为推挽输出,就不用拉高了。

2、单片机上的管脚接上拉下拉电阻的作用以及连接图

由于单片机的输出端都是开漏输出,就像三极管的集电极一样,没有上拉电阻就无法输出高电平。下拉电阻是拉低电平,和上面的相反。但在单片机中,通常有很多上拉电阻,很少有带下拉电阻的单片机。下拉电阻在单片机上真的很少见。至于上拉电阻的连接,楼上已经画好了。加上下拉电阻就是加在单片机管脚上的负载电容。比如上拉电阻的连接,就是电源通过一个阻值合适的电阻连接到需要连接的管脚上。

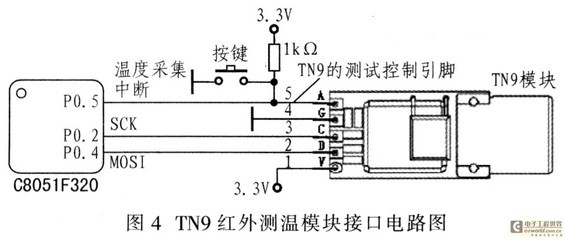

3、单片机引脚输入高电平为什么要加上拉电阻?有图,求指导。

抗干扰是设计单片机控制系统的关键。P2.1作为输入口直接接5V电源是可行的,有最好的“抗干扰”性能,但如果作为输出,会烧坏单片机,所以需要加一个限流电阻。P2.1端口内部有一个上拉电阻,为什么还要加一个外部上拉电阻?单片机内部的上拉电阻约为100K,电流约为0.05 mA,这样的小电流很容易被“干扰”成低电平,在0.5 mA的10K电阻电流上接入,可以大大提高“抗干扰”性能。

4、51单片机P0口为什么要接上拉电阻?

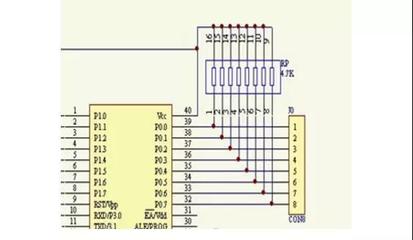

从头学起51什么是上拉电阻?为什么P0端口要加一个拉电阻?非常详细深入的讲解,不容错过。对比上面两张图,都是一个管脚的内部结构示意图,主要看锁存器和场效应管的Q和Q 端。锁存器是数字电路的知识,场管是模拟电路,不知道怎么学。图中,当控制电平极高时,场管导通,使引脚处的电位等于0,输出为0。第一张图,你看高电平的时候,P0口的引脚电流很小,应该是5mA,它的电压很小,所以必须加一个电阻,电流乘以电阻1K*5mA5V。在第二幅图中,通过关闭场管,电位等于VCC电位和5V。

5、单片机中P0口作为输出为什么要上拉电阻

由于89C51单片机的P0口内部没有上拉电阻,所以是开漏输出,需要外部上拉才能正常输出高电平。上拉电阻是一个从高电平电源引出并连接到输出端的电阻。当P0口作为IO口输出时,输出低电平为0,输出高电平为高(不是5V,相当于浮空状态)。也就是说,PO口并不能真正输出高电平给连接的负载提供电流,所以需要连接一个上拉电阻(一个电阻接在VCC上),电源通过这个上拉电阻给负载提供电流。

扩展数据:如果电平由OC(集电极开路,TTL)或OD(漏极开路,CMOS)输出,没有上拉电阻无法工作。这就很好理解了,电子管没有电源是无法输出高电平的。如果输出电流比较大,输出电平会降低(这种情况是电路中已经有一个上拉电阻,但是电阻太大,压降太高),所以可以用上拉电阻来提供电流分量,“上拉”电平。

6、单片机引脚内部上拉是什么意思

请先了解一下什么是上拉电阻。你说的单片机引脚内部上拉,是指上拉电阻不在集成电路内部,P0没有其他P口,所以需要上拉电阻,也就是接一个电阻到高电位(不悬空)。上拉表示I/O口通过电阻接VCC,默认为H,下拉表示I/O口通过电阻接GND,默认为L!上拉意味着电阻的一端连接到io引脚,另一端连接到电源,单片机,全称是SingleChipMicrocomputer,又称微控制器,是将中央处理器、存储器、定时器/计数器和各种输入/输出接口集成在一个集成电路芯片上的微型计算机。